| CATEGORII DOCUMENTE |

Universitatea Tehinca din

Catedra de Calculatoare si tehnologia informatiei

Microcalculator

simplu

Tema proiectului este implementarea structurala a unui microcalculator (un calculator simplu cu memorie limitata, cu un cuvant de instructiune de cel mult 32 biti, care executa de obicei un singur program). Pentru realizarea acestei cerinte am ales implementarea unei arhitecturi MIPS multicycle cu 2 magistrale, cu cuvantul de date si instructiune de 32 de biti, de tip load/store. Setul de instructiuni este redus (fiind o arhitectura RISC), astfel am implementat: add, sub, or, and, not, addi, lw, sw, beq, sllv, sltiu, jr. Acestea acopera tipurile de instructiuni necesare unui program simplu: operatii aritmetico-logice cu registri (primele 5 si sllv) sau date imediate (addi), salturi conditionate in caz de egalitate (beq), operatii cu memoria (lw, sw), operatii de testare de mai (sltiu) si salturi necontionate (jr).

Implementarea proiectului s-a facut in mediul de dezvoltare Xilinx ISE Webpack 9.2, iar simularea in simutorul incorporat in mediul de dezvoltare mentionat anterior. Componentele de baza ale sistemului sunt microprocesorul, memoria principala de date si de program si unitatea de intrare/iesire. Microprocesorul este la randul sau impartit in unitatea de control si caile de date. Componentele cailor de date comunica prin 2 magistrale interne, iar unitatea de control este de tip one flip-flop/state.

In ultimi ani calculatoarele au devenit parte integranta a vietii oamenilor, fiind prezente in aproape toate formele de tehnologie si in toate domeniile de activitate. Desi pana in urma cu un deceniu proiectantii incercau sa implementeze cat mai multe instructiuni in calculatoare (calcullatoare CISC=Complete Instruction Set Computer) pentru a face programarea mai usoara, acestea au devenit intre timp mult prea complexe si necesita resurse importante. La momentul actual calculatoarele CISC au fost inlocuite din aproape toate domeniile de calcultoare pe arhitectura RISC=Reduced Instruction Set Computer care au numar relative mic de instructiuni implementate ceea ce le face mai simple si mai usor de utilizat in cadrul unor sisteme integrate precum masini de spalat, telefoane mobile, diferite sisteme de asistenta devenite standard in industria auto (ESP, ABS etc.) sau procesoare digitale de semnal.

Microcalculatoarele sunt acele calculatoare de dimensiuni relative reduse , care ruleaza un singur program. Microcalculatorul, la baza este alcatuit dintr-un microprocessor sl o memorie care poate fi impartita in memorie de program si memorie de date sau poate fi comuna. Microprocesorul este "creierul" sistemului el dand comenzi celorlalte componente ale sistemului prin introduceri si extrageri de date din memorie si coordonarea diferitelor activitati concurente. In memorie sunt pastrate fie in sectiuni complet separate datele si programul (caz in care ese vorba despre o arhitectura von Neumann), fie in acelasi bloc (pentru arhitecura Harvard) datele si instructiunile programului ce trebuie executat.

Un microcalculator are un set de instructiuni redus, cu alte cuvinte stie sa faca doar lucrurile elementare cum ar fi adunari sau incarcari si extrageri de date din memorie, ori salturi. Setul de instructiuni este determinat in mare masura de domeniul apliucatiei in care va fi utilizat sistemul integrat.

Tema prezentului proiect este realizarea unui micocalculator simplu si implementarea lui pe o placa FPGA (Field Programmable Gate Array) Spartan 3 in limbajul de descriere hardware VHDL, folosind o descriere structurala a functionarii circuitului. Obiectivele acestui proiect sunt realizarea unui sistem functional, capabile sa execute instructiunile aflate in memorie si sa afiseze diferite informatii cu privire la actiunea in curs de desfasurare, cum ar fi instructiunea curenta, valoarea poantorului instructiunii curente sau continutul magistralelor.

Pentru realizarea temei proiectului am adoptat o arhitecura MIPS (Microprocessor without Interlocked Pipeline Stages) creata de MIPS, Inc. Multicycle, cu un cuvant de adresa 32 de biti si un cuvant de instructiune tot de 32 de biti. Multicycle inseamna ca o instructiune se executa in mai multe cicluri de tact. Instructiunile au dimensiune fixa de 32 de biti si se gasesc in aceeasi memorie ca si programul, iar in interiorul microporcesorului datele sunt transmise pe doua magistrale si memorate in cei 32 de registrii generali. Memoria sa este de 1 kilooctet, fara cache, iar comunicarea cu exteriorul se face prin LED-urile, intrerupatoarele si butoanele de pe placa FPGA. Instructiunile implementate sunt instructiunile aritmetico-logice( add, sub, not, or), branch, load, store si salt neconditionat.

In capitolele ce urmeaza se vorbeste in detalui despre proiectarea si testarea microcalulatorului simplu. Capitolul 2. Fundamente teoretice explica termenii si conceptele utilizate la realizarea acestui proiect. In capitolul 3. Proiectara este amanuntita descrierea solutiei gasite, prin modelele utilizate la realizare, scheme, tabele de semnale, organigrame si diagrame de timp. Capitolul Rezultate experimentale cuprinde rezultatele testelor efectuate prin diagrame de timp si tabele. Ultimul capitol este cel dedicat Concluziilor in care sunt reiterate cele mai importante idei ale raportului, subliniind

Descrierea general a unui calculator lasa o mare libertate de alegere a metodei de implementare, astfel ca procesorul poate fi impementat folosind un din multele arhitecturi disponibile pe piata, iar fiecare astfel de arhitectura vine cu un set de variante. Pentru arhitecura MIPS aleasa sunt posibile multe variatiuni in ceea ce priveste dimensiunea magistralei, numarul de cicluri pe instructiune sau numarul de registrii generali.

Procesorul poate fi implementat ca un single cycle [2], fiecare instructiune fiind executata intr-un singur ciclu de tact. Caile de date pentru un astfel de microprocessor sunt formate numai din circuite combinationale, durata unui ciclu fiind obligatoriu sa fie mai mare decat cea mai lunga cale a unei instructiuni. Acest mod de implementare are marele dezavantaj al vitezei reduse.

Chiar si in cadrul implementarii multicycle exista un numar de alternative la solutia aleasa: pot fi utilizate trei magistrale pentru a comunica intre diversele componente ale microprocesorului, dar astfel s-ar complica legarea componentelor care trebuie sa comunice cu alte componente legate la magistrale diferite. Un procesor cu o singura magistrala executa majoritatea instructiunilor intr-un timp mai mare decat in caziul solutiei cu 2 magistrale. Apoi din puncutl de vedere al numarului de registrii generali, 32 este un numar suficient pentru nevoile de calcul ale procesorului.

Procesorul MIPS este un procesor RISC de tip load/store cu o latime de adresa de 32 de biti si un cuvant de date de 32 biti si 32 de registri generali pe 32 biti, din care registrul 0 are intotdeauna valoarea 0. Poate face adresarea memoriei in 4 moduri:

registru ex. ADD R4, R3, R2 R4 ← R3 + R2

imediat ex.. ADD R1, R2, #6 R1 ← R2 + 6

deplasament: ex. LW R3, 200(R4) R3 ← MEM[200 + R4]

relativ: ex. BEQ R1, R2, #6 PC += (R1 == 0 ?

Instructiunile procesorului au lungime fixa de 32 de biti si se impart in 3 categorii: de tip R, I si J fiecare cu specificitatea sa, detaliata in continuare pentru mai multe detalii vezi [].

Instuctiunile de tip R sunt utilizate pentru operatii aritmetico-logice: add, sub, or, and sau pentru instructiunile de salt cu valoare din registru si testare diferenta dintre doua valori (in figura 1 este impartirea cuvantului de instructiune in campuri). Mai multe informtii despre MIPS la [5][3].

Fig. 1: fomatul de instructiune R

Semnificatia campurilor este:

opcod este codul operatiei, cod unic pentru toate operatiile aritmetice si logice si diferite de cel al instructiunilor de salt cu registru si testare (sllv);

rs, rt, rd adresele registrului sursa, a celui tinta si a registrului destintie din register file;

shamt reprezinta cu cat este deplasat registrul sursa (numai in operatiile de delasare cu constante puteri ale lui 2);

func cod care zice Alucontrol care operatie aritmetico-logica trebuie executata in cazul instructiunilor de tip aritmetico-logice;

Instrutiunea de tip i este intructiune in care se utilizeaza date imediate. De acest tip sunt si instructiunile de acces la memorie load si store, precum si cea de salt neconditionat. (vezi figura 2)

Fig. 2: formatul de instructiune I

Semnificatia acestor campuri este:

rs, opcode au aceleasi semnificatii ca si la formatul R; rs are semnificatia de baza in cazul load si store;

rt este adresa la care se scrie rezultatul operatiei; la branch este unul dintre operanzii scaderii pentru determinarea valorii de adevar a conditiei de salt

immediat este data imediata (constanta) pe 16 bit; pentru instructiunile aritmetice cu date imediate este al doilea operand (celalalt fiind din registru), pentru load si store este deplasamentul adresei de memorie unde se face scrierea sau se citeste, iar in cazul instructiunii branch (salt conditionat) este deplasamentul fata de adresa instructiunii curente unde se face salt

Instructiunea fde tip j este folosita la instructiunile de salt neconditionat (fig. 3):

Fig. 3: formatul de instructiune J

Semnificatia campurilor este:

opcode la fel ca la celelalte formate

target este deplasamentul cu care se face saltul relativ

Urmatoarea etapa este operand fetch. Ea depinde de instructiune dar de obicei se incarca unul dintre operanzi in registrul auxiliar RB sau in MAR ori MDR depinde de instructiune

Executia instructiunii consta in efectuarea modificarilor specifice fiecarei instructiuni(adunarea operazilor, scrierea in memorie, incarcare din memorie in register file salt la instructiunea de la adresa data etc.). Dupa aceasta etapa urmeaza depunerea rezultatului obtinut in memories au in register file - write back.

Conform [2] un calculator are la baza o structura la fel ca in figura 4, cu un microprocesor, o memorie de date si program, o interfata cu exteriorul (module periferice), si interconexiunile intre acestea: magistralele de date si de adrese.

Figura 4: structura unui calculator simplu

Implementarea sistemului s-a facut in mediul de dezvoltare Xilinx ISE Webpack 9.2 al firmei Xilinx si pe placa Digilent Basys cu FPGA Spartan 3.

Microprocesorul este componenta fundamental a oricarui sistem de calcul. El are o arhitectura MIPS multicycle cu 2 magistrale [4]. Setul de instructiuni este unul redus la minimul necesar fiind format din instructiuni aritmetico-logice cu registri si cu date imediate, load, store, jump register, shift left variable, set less then immediate si branch equal.

Fiind un caclculator RISC, setul de instructiuni este redus la mnimul necesar. Arhitecura setul de instructiuni (ISA) a acestui procesor contine 12 instructiuni: add, sub, and, or, not, sllv, jr, sltiu, addi, beq, lw si sw. Codurile de operatii pentru aceste instructiuni pot fi vazute in tabelul din fig. 5

|

Cod |

Operatie |

|

Operatie aritmetico-logica (add, sub, and, or, not) |

|

|

Adunare cu data imediata (addi) |

|

|

Load word (lw) |

|

|

Store Word (sw) |

|

|

Salt conditionat (beq) |

|

|

Salt neconditionat (jr) |

|

|

Deplasare cu valoare varibila (sllv) |

|

|

Comparatie < (sltiu) |

Fig. 5: tabelul codurilor de operatie

Inainte fiecarei instructiuni se executa instruction fetch. Astfel instructiunea este incarcata in registrul de instructiuni din memorie. Etapele concrete ale acestui process sunt prezentate mai jos in RTL concret (pe coloana din dreapta sunt semnalele de control activate pe parcursul efectuarii pasului respectiv):

T0: MAR<-PC

T1: MDR<-M(MAR)

PC<-PC+4

T2: IR<-MDR

Instructiunile and, or, not, add, sub sunt instructiuni de tip R cu acelasi cod de operatie, diferentierea operatiei facandu-se in functie de valoarea campului func care e decodificata in unitatea de control a unitatii aritmetico-logice. In notatie RTL abstract o instructiune de acest tip are forma:

R(rd)<-R(rs) op R(rt), unde op este +, -, and, or

Iar mnemonica sa este

Instr rd, rt, rs

Un cazul particular este intructiunea not care are un singur operand si atunci notatia RTL pentru aceasta este:

R(rd)<- not R(rt).

Aceste instructiuni se executa in mai multi pasi dupa cum urmeaza:

T3: RA<-R(rs)

T4: R(rd)<-RA op R(rt)

Valorile campului func pot fi cele din tabelul urmator (fig. 6):

|

Cod |

Operatie |

|

Adunare |

|

|

scadere |

|

|

Or |

|

|

And |

|

|

Not |

|

|

Shift |

Fig. 6: valorile si semnificatiile campului func

Alte instructiuni de tip R sunt

sllv si jr

Instructiunea sllv este o

instructiune de deplasare a unei valori continute in registrul R(rs)

de atatea ori cat indica registrul R(rt). Mnemonica si scrierea RTL

abstracra sunt:

R(rd)<-R(rs) << R(rt)

Sllv rd, rs, rt

Fazele acestei instructiuni difera insa de cele ale celorlalte instructiuni de tip R; se comporta dupa cum urmeaza:

T3: RA<-R(rs)

T4: SCNT<-R(rt)

T5 & ZSC=0: R(rd) <- RA << 1

SCNT<- SCNT -1

Repeat T5

T5 & ZSC=0: end

ZSC este flagul de zero care indica executarea numarului dorit de deplasari cu o pozitie.

Instructiunea jr este o alta instructiune de tip R speciala, ea oferind o modalitate de a executa salt neconditionat la o adresa de instructiune continuta in registrul R(rs). Mnemonica instructiunii este:

jr R(rs),

iar definitia sa in RTL este:

PC<- R(rs).

Pasii aceste instructiuni sunt:

T3: PC<-R(rs).

Instructiunile de tip I sunt

mai diverse dar elementul comun este cel ca folosesc o valoare constant

pentru a executa operatia dorita. Aceste instructiuni sunt addi,

lw, sw, beq, sltiu. In aceste caz registrul destinatie al operatiei

devine rt.

Instructiunea lw

efectueaza incarcarea din memorie a valorii (cuvantului) de la adresa

obtinuta prin adunarea bazei data de valoare registrului R(rs)

adunata cu deplasamentul dat de constanta continuta in campul

immediate al instructiunii in registrul R(rt). Mnemonica si RTL

(abstract si concret) sunt dupa cum urmeaza:

lw rt, rs(immediate)

R(rt)<-M(R(rt)+immediate)

T3: RA<-R(rs)

T4: MAR<-RA + Sign x Immediate

T5: MDR<-M(MAR)

T6: R(rt)<-MDR

Instructiunea omolog a lui lw este sw care depune in memorie la adresa calculata ca la lw valoarea continuta de registrul R(rt):

sw rt, rs(immediate)

M(R(rs)+immdiate)<-R(rt)

T3: RA<-R(rs)

T4: MAR<-RA+ Sign x Immediate

T5: MDR<-R(rt)

T6: M(MAR)<-MDR

Operatia aritmetica de adunare cu un numar este facuta de addi:

addi rt, rs, immediate

R(rt)<-R(rs)+Sign x immediate

T3: RA<-R(rs)

T4: R(rt)<- R(rs)+immediate

Pentru controlul fluxului programului este introdusa instructiunea de salt conditionat beq. Daca valorile din registrii R(rs) si R(rt) sunt egale, conditia este satisfacuta si urmatoarea instructiune seexecuta de la adresa PC + Sign x immediate

Beq rs, rt, immediate

if R(rs)=R(rt) then PC<-PC+Sign x immediate

T3: RA<-R(rs)

T4: Z<-Zero(RA, R(rt))

T5 & Z='0': end

T5 & Z='1' RA<-PC

T6 & Z='1' PC<-RA + Sign x immediate<<2

Instructiunea sltiu este cea care scrie 1 in registrul R(rt) daca R(rs)<Sign x immediate altfel scrie 0.

sltiu rt, rs, immediate

if R(rs)<Sign x immediate then R(rt)<-00001h

else R(rt)<- 00000h

T3: RA<-R(rs)

T4: R(rt)<- comp(RA, Sign x immediate)

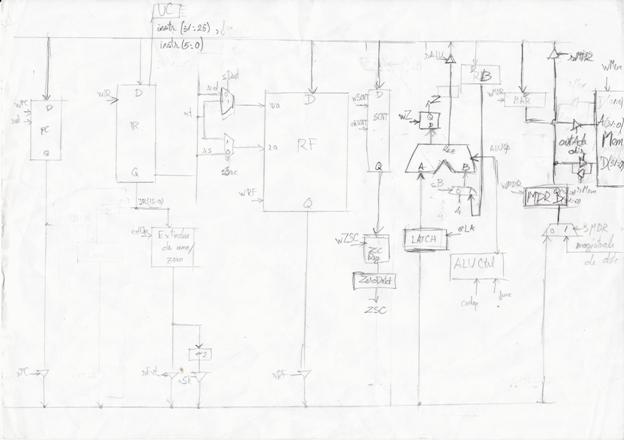

Caile de date sunt circuitele prin care circula informatiile propriu-zise: date sau instructiuni aflate in executie. Pentru a putea realiza operatiile imlpementate caile de date contin o unitate aritmetico-logica, un register file (32 de registri generali) un registru contor de program (program counter) si un registru de instructiune, precum si alte componente care vor fi detalate in continuare.

Fig. 7: caile de date

Principalele componente ale cailor de date sunt:

Progrma counter: retine adresa instructiunii curente,

IR:: registrul instructiunii curente; de aici au pleca spre caile de date func si codop

RF: 32 de registi generali pe 32 biti

ALU: unitatea aritmetico-logica care calucleaza face operatiile adunare, scadere, si logic, negatie logica, sau logic, test de mai mic si deplasare la stanga cu o pozitie. Valorile pentru aluOp pentru fiecare operatie sunt in tabelul

|

Operatie |

Valoare aluOp |

|

Adunare | |

|

Scadere | |

|

Deplasare la stanga | |

|

Si logic | |

|

Sau logic | |

|

Negare | |

|

Mai mic | |

|

Nici o operatie |

Fig. 8: valorile aluOp pentru fiecare opratie aritmetico-logica

SCNT: numarator pentru operatia deplasaril; continte numarul de deplasari care trebuie efecutate;

MDR: registrul de date in comunicarea cu memoria princpala

MAR: registrul de adrese in comunicarea cu memoria principal

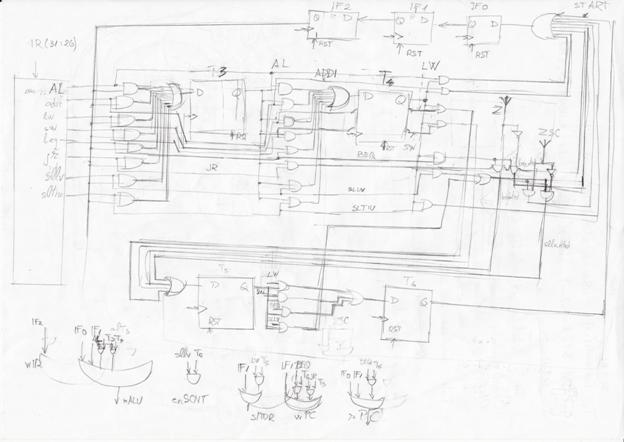

Unitatea de control genereaza semnalel de comnda si control pentru caile de date si memorie. Am optat pentru o unitate de control implementata prin metoda one flip-flop/state care esteu usor de implementat pe o placa FPGA. Schema bloc este:

Fig, 9: unitatea de control cu bistabil pe stare

Semnalele de control sunt generate prin sau intre starile in care trebuie sa fie active. Valorile semnale pentru fiecare stare se afla in anexa 1. Pentru resetare sistemul trece printr-o stare de sincronizare inainte de a intra in instruction fetch.

Avand o arhitectura de tip Harvard deci este format dintr-un singur bloc atat instructiunile cat si datele. In memorie, la adresa 0000h se afla prima instructiune care se incarca in caile de date la semnalul de start. Schema bloc este in fig. 10.

Fig.10: schema bloc a memoriei

![]()

Intrarea si iesirea din acest sistem a informatiilor se face prin LED-urile de pe FPGA si afiseaza starea curenta a sistemului. Pentru vizuializarea diferitelor informtii se folosesc cele 4 unitati de afisare cu 7 segmente. Deoarece cuvantul de instructiune si cel de date este de 32 de biti, se poate afisa la un moment dat o singura valoare pe astfel ca este necesara selectia carei date se afiseaza prin switch-urile de pe placa. Pornirea executiei se face de la buton de start (butonul 0), iar resetarea se face asincron de la un butonul de reset (butonul 1).Porturile pentru comunicatia cu exteriorul ar trebui adaugate pentru a da functionalitate deplina acestui microcalculator, adica sa poata comunica cu alte componente.

Pentru a introduce date in caclulator trebuie inscris in memorie RAM programul dorit si datele necesare exedcutarii lui

La testarea sistemului si subsistemelor sale am utilizat simulatorul Xilinx ISE integrat in mediul de dezvoltare Xilinx ISE Webpack 9.2.

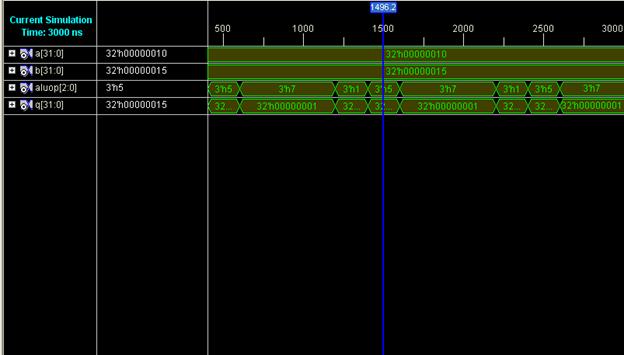

In sectiunea de testare am testat individual fiecare componenta importanta. Prima astfel de componenta testata este unitatea aritmetico-logica

Fig, 11: simularea unitatii aritmetico-logice

Pentru simularea unitatii aritmetico-logice am laut 2 numere la intamplare, anume 10h si 15h si am modificat valorile aluOp pentru a simula mai multe opratii. Prima operatie este testarea de mai mic, in acest caz se evalueaza 10<15 si rezultatul, asa cum reiese si din fig. 11 este 1h deoarece 10<15. Api urmeaza adunarea cu rezultatul de 25h, din nou cel corect. Ultima operatie este un sau logic care are ca rezultat valoare 15h deoarece 0 sau 5 rezulta 5.

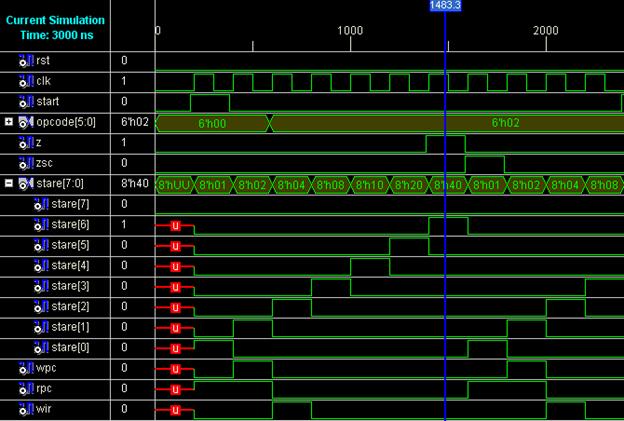

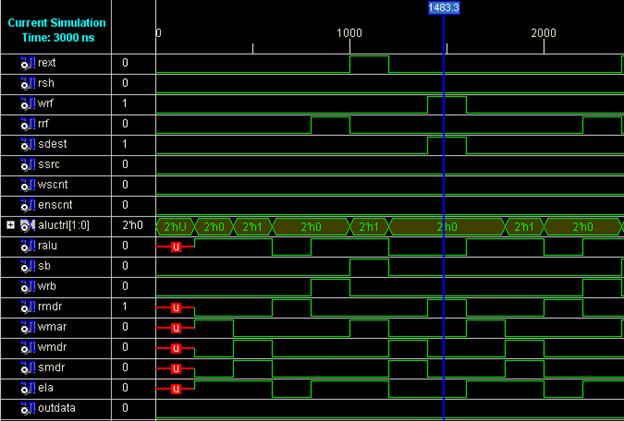

Simularea unitatii de control presupune introducerea unei intructiuni si urmarirea valorii fiecarui semnal de control dupa tabelul din anexa 1. Am simulat o operatie de load word care are 6 faze inclusiv instruction fetch. Rezultatele sunt in figurile 12 si 13. Dupa cum se observa din compararea valorilor de pe simulare cu cele din tabel ca aceasta componenta functioneaza corect.

Fig. 12: simularea unitatii de control, partea superioara a semnalelor

Fig. 13: simularea unitatii de control, partea inferioara a semnalelor

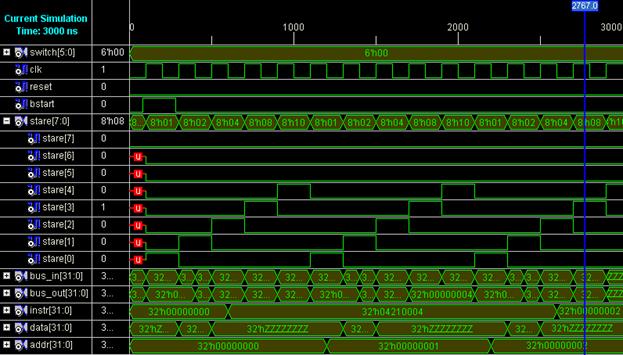

Simulare finala intregului sistem pentru o secventa de instructiuni s-a facut dupa integrarea cailor de date cu unitatea de control si memoria principala, iar simularea apare in forma urmatoare (fig. 14):

Fig. 14: simularea sistemelui

Prima instructiune este addi r(1), r(0), 4, iar a 2-a este la fel.

[1] Baruch, Zoltan Francisc "Arhitectura calculatoarelor" Cluj-Napoca 2000

[2] Nedevchi, Sergiu "AC-introducere", cursuri arhitecura calculatoarelor Universitatea Tehinic din Cluj-Napoca, 2008

[3] Nedevchi, Sergiu "MIPS ISA", cursuri arhitecura calculatoarelor Universitatea Tehinic din Cluj-Napoca, 2008

[4] Nedevchi, Sergiu "Bus_MIPS ", cursuri arhitecura calculatoarelor Universitatea Tehinic din Cluj-Napoca, 2008

https://6004.csail.mit.edu/6.371/handouts/mips6371.pdf

|

Politica de confidentialitate | Termeni si conditii de utilizare |

Vizualizari: 4806

Importanta: ![]()

Termeni si conditii de utilizare | Contact

© SCRIGROUP 2026 . All rights reserved