| CATEGORII DOCUMENTE |

Interfete programabile

1. Introducere

Dupa cum a fost prcizat in capitolele anteriaoare, unitatea centrala de procesare intr-un sistem cu microprocesor, comunica cu mediul exterior prin asa numitele porturi sau interfete, ce permit conversia sau adaptarea semnalelor externe la numere pe magistrala de date, numere ce pot fi prelucrate intern. Exista

- interfete pentru semnale logice (numerice), asa numitele porturi paralele sau numerice,

- interfete pentru semnale analogice (continue)- convertoare analog-numerice si numeric-analogice,

interfete de numarare si temporizare (timere),

interfete de comunicare seriala cu alte echipamente numerice.

In acest capitol vor fi prezentate cateva circuite specializate, programabile, care indeplinesc aceste functii, de interfatare a sistemului cu microprocesor cu mediul exterior. Ele au fost realizate in anii 80de firma Intel, si au fost destinate echiparii sistemelor cu microprocesoare de prima generatie (I8080), insa, datorita performantelor lor remarcabile, echipeaza si astazi, cu mici modificari, placile cu microprocesor.

2. Interfata seriala programabila 8251

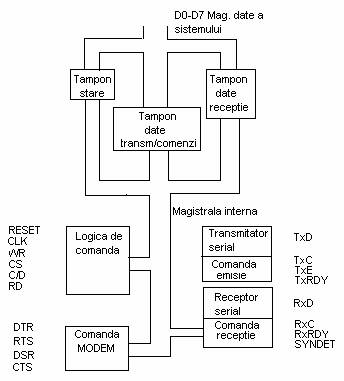

Interfata seriala programabila (USART- Universal Synchronous-Asynchronous Receiver Transmitter) este un circuit (vezi fig.1.)ce accepta date sub forma de caractere , transmise in paralel de catre unitatea centrala, le converteste intr-un format serial si le transmite catre un destinatar. Totodata, poate recptiona date sub forma seriala de la un emitator, le converteste in caractere si le transfera paralel catre unitatea centrala.

Pentru a realiza acestea, 8251 are in structura sa blocurile prezentate in fig.2 .

Frecventa comunicatiei (de bit) este generata catre 8251 de la un timer. Frecventa de bit a emitatorului trebuie sa fie identica cu frecventa de bit a receptorului. Totusi este necesara o sincronizare pentru a alinia fazele. Sincronizarile se fac diferit in functie de modurile de lucru.

Are doua de lucru

de baza - sincron si asincron. In modul sincron datele sunt transmise sau

receptionate in blocuri, sincronizarea facandu-se prin caractere speciale de

sincronizare SYN transmise dupa un numar oarecare de biti. In modul asincron,

este transmis sau receptionat un singur caracter de 5,6,7 sau 8 bit, incadrat

la inceput de un bit de START, cu rol de sincronizare, si la sfarsit de un bit de paritate (daca e

cazul) si de 1 sau 2 bit de STOP.

Circuitul 8251 contine un registru de comanda (care se scrie), un registru de stare (care se citeseste) si un registru de date (fizic sunt doua locatii dar cu aceeasi adresa, una pentru transmisie si una pentru receptie). El este programat prin 2 cuvinte de comanda succesive, primul cuvint de comanda este primul transmis catre circuit dupa RESET, si are functia de selectare a modului de lucru. Dupa acesta, toate cuvintele de comanda au rolul de tratare a comunicatiei.

Starea comunicatiei este citita din registrul de stare.

Datele sunt trimise catre 8251 (pentru transmisie) sau citite (de la receptie) din registrul de date.

Adresarea se face conform tabelului.

|

-CS |

C/-D |

-RD |

-WR |

Functia |

|

Citire data de unitatea centrala |

||||

|

Citire stare |

||||

|

Scriere data |

||||

|

Scriere comanda |

||||

|

x |

x |

x |

Circuit neselectat |

|

Terminal |

Descriere |

Tip |

|

D0-D7 |

Conexiuni la magistrala de date a microsostemului |

In-Out |

|

RESET |

Aducere in conditii initiale |

In |

|

CLK |

Ceasul dispozitivului |

In |

|

C/-D |

Selectie comanda-data |

In |

|

-RD |

Citeste data sau starea |

In |

|

-WR |

Scrie comanda sau data |

In |

|

-CS |

Selectie circuit |

In |

|

-DSR |

Modem pregatit |

In |

|

-DTR |

Interfata pregatita pentru comunicatie cu modem |

Out |

|

-CTS |

Acceptare transmisie de la modem |

In |

|

-RTS |

Cerere de transmisie catre modem |

Out |

|

TxD |

Iesire seriala de date |

Out |

|

TxRDY |

Circuit pregatit de a primi date pe magistrala pt Tr |

Out |

|

TxE |

Circuit gol (nu mai are date de transnmis) |

Out |

|

-TxC |

Clock pentru transmisia seriala |

Out |

|

RxD |

Intrarea seriala |

In |

|

RxRDY |

Caracter pregatit pentru a fi transmis pe mag. date |

Out |

|

-RxC |

Clock pentru receptia seriala |

In |

|

SYNDET |

Detectie sau fortare caracter sincronizare |

In-Out |

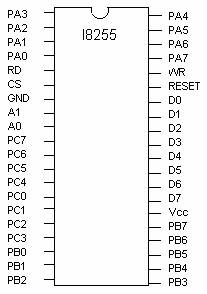

3. Interfata paralela programabila 8255

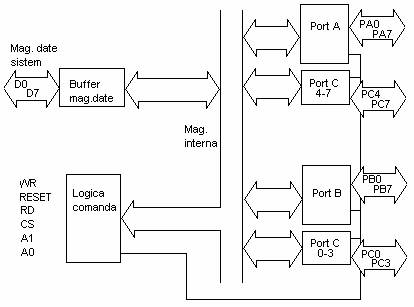

Circuitul 8255 reprezinta o interfata paralela (numerica) pentru citirea/scrierea semnalelor logice la/de la mediul exterior. El contine 24 terminale ce pot fi configurate ca 3 porturi de 8 bit bidirectionale.

Configuratia pinilor este prezentata in fig. 3 cu descrierea pinilor in tabel, iar in fig.4

|

Terminal |

Descriere |

Tip |

|

D0-D7 |

Magistrala de date bidirectionala |

In-Out |

|

PA0-PA7 |

Port A |

In-Out |

|

PB0-PB7 |

Port B |

In-Out |

|

PC0-PC7 |

Port C |

In-Out |

|

-RD |

Comanda citire |

In |

|

-WR |

Comanda scriere |

In |

|

RESET |

RESET, aducere registri la starea initiala |

In |

|

-CS |

Selectie circuit |

In |

|

A0, A1 |

Intrari selectie porturi |

In |

Circuitul 8255 poate lucra in 3 moduri.

Modul 0 este modul de intrare iesire in care se scrie o data in registrul de data corespunzator portului, iar aceasta este plasata pe liniile portului de iesire. La citire, data primita pe linmiile portului de intrare este citita de la registrul de date cu o instructiune de citire.

Modul 1 (asemanator cu modul 2) permite o conversatie cu un dispozitiv corespondent. Astfel, la citire (intrare), dispozitivul extern plaseaza un cuvant pe liniile portului A si activeaza semnalul -STBA. Circuitul 8255 preia continutul liniilor si le depune intr-un registru de date, activand semnalul IBFA care indica faptul ca datele sunt in registru. Totodata genereaza si o intrerupere catre unitatea centrala pe linia -INTRA. Microprocesorul citeste continutul registrului de date inactivand linia -IBFA si permitand inceperea unui nou ciclu. La scriere in exterior (iesire), circuitul 8255 plaseaza un caracter pe liniile portului A, generand semnalul -OBFA. Circuitul destinatar este semnalizat de semnalul -OBFA, preia datele si raspunde cu semnalul -ACK. Acesta inactiveaza -OBFA si genereaza intrerupere catre microprocesor pentru a transmite un nou caracter. Semnalele sunt prezentate in fig. 5.

Fig.5. Semnalele la circuitul 8255 in modul de lucru 1

Pentru programarea si transferul datelor de la si catre circuitul 8255, acesta contine 3 registri de date, cate unul pentru fiecare port, care pot fi cititi si scrisi, si un cuvant de comanda ce poate fi scris. Selectia acestora se face cu bitii A0 si A1 conform tabelului urmator.

|

-CS |

A1 |

A0 |

-RD |

-WR |

Functia |

|

|

Scriere data de unitatea centrala la portul A |

||||

|

Scriere data de unitatea centrala la portul B |

|||||

|

Scriere data de unitatea centrala la portul C |

|||||

|

Scriere data de unitatea centrala in registrul de comanda |

|||||

|

Citire data de unitatea centrala de la portul A |

|||||

|

Citire data de unitatea centrala de la portul B |

|||||

|

Citire data de unitatea centrala de la portul C |

|||||

|

x |

x |

x |

Circuit neselectat |

5. Arbitrul de intreruperi programabil 8259

Arbitrul de intreruperi este un circuit ce poate manipula pana la 8 cereri de intrerupere externa asigurand o varietate de modalitati programabile pentru arbitrarea prioritatilor acestora. Pentru a creste numarul de intreruperi gestionate la 64, 8 circuite 8259 pe post de slave pot fi conectate la un circuit 8259 master.

Configuratia pinilor este prezentata in fig.6, iar structura interna este prezentata in fig.7.

Fig.6. Configuratia pinilor la circuitul 8259

Fig.7. Structura interna a circuitului 8259

O cerere de intrerupere de la o sursa externa pozitioneaza pe 1 un bistabil din Registrul Cererilor de intrerupere (RCI). Pozitionarea pe 1 a unuia sau mai multor bistabili din RCI duce la generarea unui semnal de intrerupere INT catre microprocesor. Raspunsul INTA pune pe 0 bistabilul cererii care uremeaza sa fie tratata si pozitioneaza pe 1 un bistabil in Registrul Cererilor de intrerupere tratate (RCIT). Acest bit va fi adus la 0 dupa ce se incheie rutina de tratare a intreruperii. Circuitul pentru rezolvarea prioritatilor stabileste care este intreruperea ce va fi tratata in functie de prioritatile prestabilite.

Semnalul de recunoastere a intreruperii INTA face ca 8259 sa forteze pe liniile de date codul instructiei CALL, circuitul specializat 8228 va genera inca 2 semnale INTA iar 8259 fa forta pe liniile de date adresa rutinei de intrerupere.

Registrul de mascare a intreruperilor va masca intreruperile ce trebuie invalidate accesand bitii din RCI si RCIT.

|

Terminal |

Descriere |

Tip |

|

D0-D7 |

Magistrala de date bidirectionala |

In-Out |

|

A0 |

Identifica unitatea ca port de I/O sau celula de memorie |

In |

|

-IOR |

Semnal de citire |

In |

|

-IOW |

Semnal de scriere |

In |

|

INT |

Semnal de intrerupere trimis de 8259 |

Out |

|

-INTA |

Recunoastere intrerupere |

In |

|

C0, C1, C2 |

Linii de selctie a 8259 slave |

Out catre master |

|

SP |

Identifica 8259 ca master sau slave |

In |

|

Politica de confidentialitate | Termeni si conditii de utilizare |

Vizualizari: 2552

Importanta: ![]()

Termeni si conditii de utilizare | Contact

© SCRIGROUP 2026 . All rights reserved