| CATEGORII DOCUMENTE |

Instrumente software

1 Mediul Integrat Xilinx ISE

1.1 Prezentare

Pachetul de programe Xilinx ISE produs de Xilinx Inc. reprezinta un mediu integrat utilizat pentru proiectarea sistemelor digitale cu FPGA-uri sau CPLD-uri produse de aceeasi companie. In general, pachetul Xilinx ISE permite utilizarea urmatoarelor tipuri de circuite FPGA si CPLD Xilinx:

Circuite FPGA din familia Spartan: Spartan-2, Spartan-2E, Spartan-3;

Circuite FPGA din familia Virtex: Virtex-E, Virtex-2, Virtex-2 Pro;

Circuite CPLD din familia XC9500: XC9500, XC9500XL, XC9500XV;

Circuite CPLD din familia CoolRunner: CoolRunner XPLA

Pentru o mai buna deservire a nevoilor diferitilor clienti, compania Xilinx Inc. ofera trei versiuni ale programului Xilinx ISE. Urmarind tabelul 1 se pot observa diferentele dintre acestea.

|

Caracteristica |

ISE WebPack |

ISE BaseX |

ISE Foundation |

|

|

Pret | ||||

|

Circuite |

Seria Virtex |

Virtex-E: XCV50E -XCV300E Virtex-II: XC2V40 - XC2V250 Virtex-II Pro: XC2VP2 Virtex-4: LX: XC4VLX15, XC4VLX25 |

Virtex: XCV50 - XCV600 Virtex-E: XCV50E - XCV600E Virtex-II: XC2V40 - XC2V500 Virtex-II Pro: XC2VP2 - XC2VP7 Virtex-4 LX: XC4VLX15, XC4VLX25 SX: XC4VSX25 FX: XC4VFX12 |

Toate |

|

Seria Spartan |

Spartan-II: All Spartan-IIE: XC2S50E - XC2S300E Spartan-3: XC3S50 - XC3S1500 Spartan-3E: XC3S100E - XC3S500E Spartan-3L: XC3S1000L, XC3S1500L |

Spartan-II: All Spartan-IIE: All Spartan-3: XC3S50 - XC3S1500 Spartan-3E: All Spartan-3L: XC3S1000L, XC3S1500L |

Toate |

|

|

CoolRunner XPLA3 CoolRunner-II CoolRunner-IIA |

Toate |

Toate |

Toate |

|

|

XC9500 Series |

Toate |

Toate |

Toate |

|

Caracteristica |

ISE WebPack |

ISE BaseX |

ISE Foundation |

|

|

Instrumente de proiectare |

Schematic and HDL Editor |

Da |

Da |

Da |

|

State Diagram Editor |

doar pentru Microsoft Windows |

doar pentru Microsoft Windows |

doar pentru Microsoft Windows |

|

|

CORE Generator |

Nu |

Da |

Da |

|

|

RTL & Technology Viewers |

Da |

Da |

Da |

|

|

PACE (Pinout & Area Constraint Editor) |

Da |

Da |

Da |

|

|

Architecture Wizards |

Da |

Da |

Da |

|

|

Xilinx System Generator for DSP |

Nu |

Optiune separata |

Optiune separata |

|

|

EDK |

Nu |

Optiune separata |

Optiune separata |

|

|

Instrumente |

XST |

Da |

Da |

Da |

|

de |

Leonardo Spectrum |

EDIF in Linux |

EDIF in Linux |

EDIF in Linux |

|

sinteza |

|

Interfata integrata |

Interfata integrata |

Interfata integrata |

|

Mentor Graphics Precision Physical |

EDIF |

EDIF |

EDIF |

|

|

Synopsys Compiler |

EDIF |

EDIF |

EDIF |

|

|

Synplicity Synplify/Pro |

Interfata integrata |

Interfata integrata |

Interfata integrata |

|

|

Synplicity Amplify Physical Synthesis |

EDIF |

EDIF |

EDIF |

|

|

ABEL |

CPLD |

CPLD |

CPLD |

|

|

Implementare |

FloorPlaner |

Da |

Da |

Da |

|

Plan Ahead |

Nu |

Optiune separata |

Optiune separata |

|

|

Timing Driven Place & Route |

Da |

Da |

Da |

|

|

Modular Design |

Nu |

Da |

Da |

|

|

Incremental Design |

Da |

Da |

Da |

|

|

Timing Improvement Wizard |

Da |

Da |

Da |

|

|

Programare |

Impact |

Da |

Da |

Da |

|

Verificare |

ChipScope Pro |

Optiune separata |

Optiune separata |

Optiune separata |

|

Graphical Testbench Editor |

doar Microsoft Windows |

doar Microsoft Windows |

doar Microsoft Windows |

|

|

ISE Simulator Lite |

Nu |

Da |

Da |

|

|

ISE Simulator |

Nu |

Nu |

Optiune separata |

|

|

ModelSim XE III Starter |

Da |

Da |

Da |

|

|

ModelSim XE III |

Optiune separata |

Optiune separata |

Optiune separata |

|

|

Static Timing Analyzer |

Da |

Da |

Da |

|

|

FPGA Editor with Probe |

Nu |

Da |

Da |

|

|

ChipViewer |

Da |

Da |

Da |

|

|

XPower (Power Analysis) |

Da |

Da |

Da |

|

|

SMARTModels |

Nu |

Da |

Da |

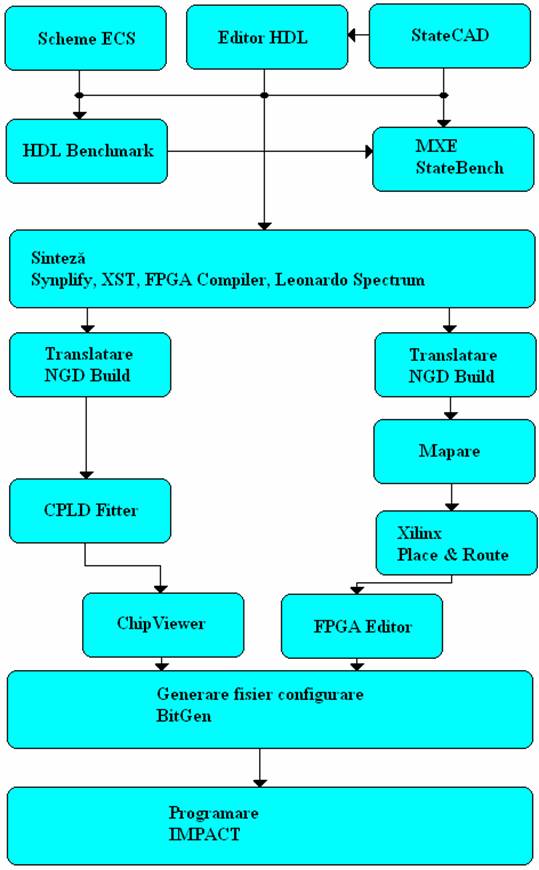

Figura 1. prezinta principalele module software ale pachetului integrat Xilinx ISE

1.2 Project Navigator

Toate programele ce compun pachetul Xilinx ISE pot fi lansate sau folosite cu ajutorul programului numit 'Xilinx Project Navigator'. Acest IDE permite crearea unor proiecte noi, vizualizarea si editarea fisierelor de intrare, a celor intermediare sau a celor generate drept iesire. Se pot genera diverse fluxuri de intrare-iesire si se pot configura FPGA-urile sau CPLD-urile tinta.

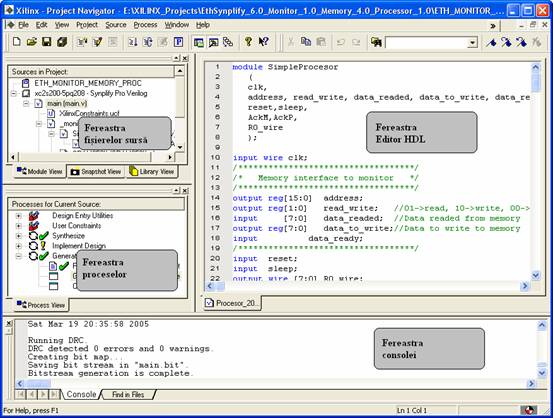

Ecranul interfetei grafice Project Navigator este impartit in patru ferestre principale, dupa cum se ilustreaza in Figura 2:

In fereastra fisierelor sursa se afiseaza toate fisierele sursa care au fost incluse in proiectul curent. Prin executia unui clic dublu pe numele unui fisier din aceasta fereastra se va deschide fisierul respectiv de catre modulul CAD corespunzator. Fereastra proceselor indica toate procesele care sunt disponibile pentru un anumit tip de fisier sursa. Executia unui clic dublu pe numele unui proces va lansa in executie procesul respectiv. Fereastra editorului HDL afiseaza continutul fisierului sursa selectat, continand descrierea unei componente digitale intr-un limbaj de descriere hardware. Continutul fisierului poate fi editat in aceasta fereastra. In fereastra consolei se afiseaza toate mesajele care indica starea executiei unui proces, inclusiv mesajele de avertisment sau de eroare care sunt generate in urma executiei. Pe langa aceste ferestre principale, interfata 'Project Navigator' poate deschide si alte ferestre necesare pentru unele aplicatii.

Fig. 2 Project Navigator

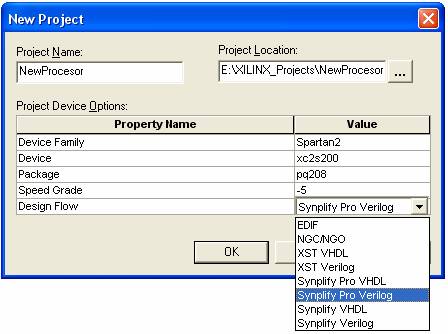

Cu ajutorul IDE-ului 'Project Navigator' se pot crea fisiere proiect noi, pentru care se pot specifica urmatoarele proprietati:

numele si locatia proiectului

tipul de FPGA sau CPLD (CoolRunner, Spartan 2, Spartan 3, XC9500)

tipul de 'package' (FG256, FG456, PQ208, etc.)

tipul de sursa sinteza aleasa (EDIF, XST, Synplify, Leonardo Spectrum, etc.)

Fig. 3 Fereastra 'New Project

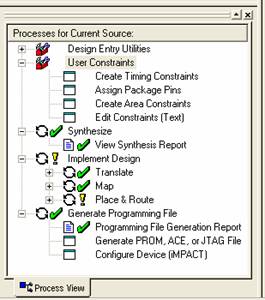

Fereastra proceselor poate fi folosita pentru a modifica o serie de parametrii cum ar fi:

Fig. 4 Fereastra proceselor

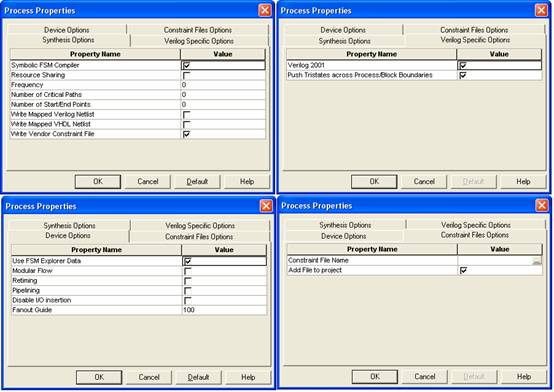

Tab-ul 'Synthesize' poate fi folosit pentru a modifica o serie de parametri folositi la sinteza circuitului electric digital (specifici instrumentului de sinteza ales) cum ar fi:

Fig. 5 Optiuni de sinteza

Dupa cum vom vedea mai tarziu (subcapitolul 2 Instrumente de sinteza), sinteza este procesul cel mai important ce are loc atunci cand un proiect este compilat. Tipul programului de sinteza, performantele acestuia vor determina decisiv pretul final al circuitului electric digital precum si performantele acestuia.

Folosirea unor optiuni precum 'Symbolic FSM Compiler Resource Sharing Use FSM Explorer Data Retiming Pipelining' poate duce la o arie (sau numar de porti) folosita mai mica si deci la un pret final mult mai mic. Cu toate acestea, nu intotdeauna aceste optiuni sunt indicate, o analiza atenta a circuitului putand arata care optiuni sunt indicate pentru proiectul actual si care nu. Dupa finalizarea procesului de sinteza un raport al acestuia va fi generat.

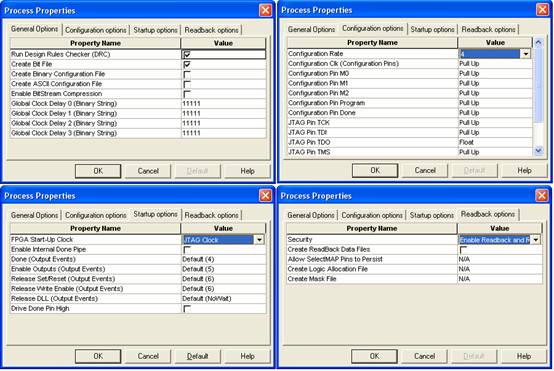

Tab-ul 'Generating Programming File' poate fi folosit pentru a modifica o serie de parametri ai fiserului final pentru configurare FPGA sau CPLD cum ar fi:

Fig. 6 Generating Programming File

1.3 Editorul de constrangeri

Pachetul Xilinx ISE permite specificarea constrangerilor de tipuri diferite pentru proiectul actual, cum ar fi:

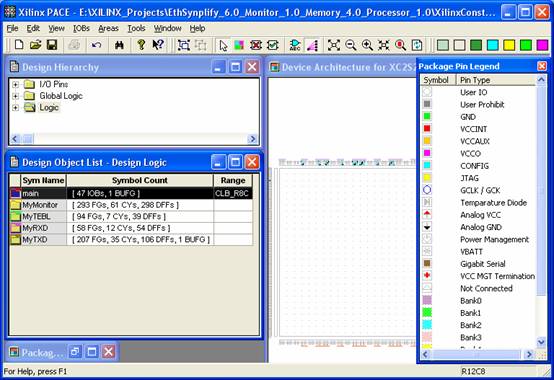

Editorul de constrangeri poate fi folosit atat in mod text in cadrul programului 'Project Navigator'cat si in mod grafic (Figura 7):

Fig. 7 Editorul de constrangeri

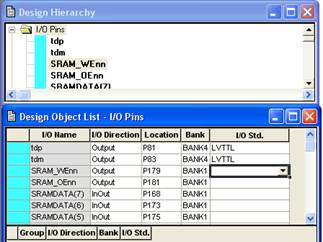

Imediat dupa incheierea procesului de sinteza, pachetul software Xilinx ISE lanseaza in fundal programul 'place & route' ce va definitiva circuitul digital curent. Acest program foloseste constrangerile definite cu ajutorul 'Constraints Editor'. Cele mai importante constrangeri ale unui proiect sunt cele legate de plasarea porturilor de I/O folosite de circuitul curent. Dupa cum se poate observa si din figura 8, se pot specifica diversi parametri cum ar fi:

Fig. 8 Parametri pentru porturi I/O

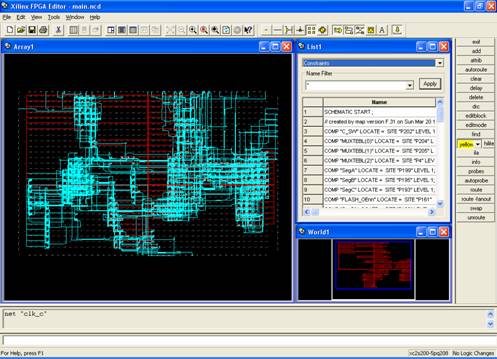

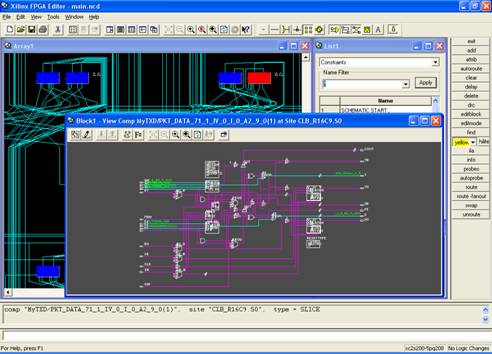

1.4 Programul 'FPGA Editor'

Pentru a verifica sau modifica fisierul binar rezultat in urma compilarii proiectului curent se poate folosi programul 'FPGA Editor'. Cu ajutorul acestui utilitar se pot incarca diversele imagini ale circuitelor implementate in FPGA-uri (figura 9):

Fig. 9 FPGA Editor

2 Instrumente de sinteza

Daca programele de 'place & route' sunt intotdeauna dezvoltate de firmele producatoare de FPGA-uri sau CPLD-uri din motive de protectie impotriva tentativelor de 'reverse engineering', programele de sinteza ale circuitelor digitale sunt dezvoltate de mai multe companii. Unele din produsele cele mai cunoscute de sinteza hardware sunt:

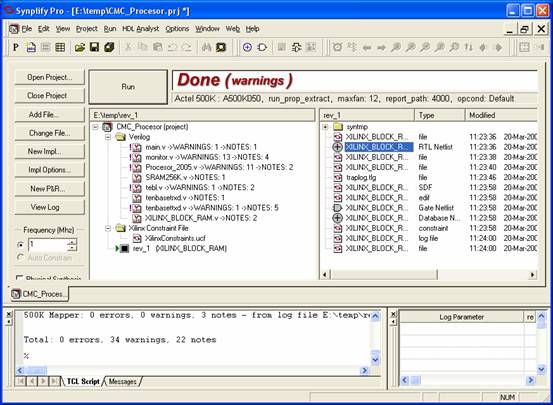

Din punctul de vedere al rezultatelor procesului de sinteza, Synplify Pro este programul cel mai performant. Daca luam in considerare pretul produsului software programul XST al companiei Xilinx Inc. este de preferat datorita faptului ca poate fi descarcat fara plata de pe site-ul companiei producatoare.

Fig. 10 Synplify Pro

Programul Synplify Pro (figura 10) este de departe cel mai performant program de sinteza hardware pentru circuitele de tip FPGA sau CPLD moderne. Cu ajutorul sau am reusit implementari ale SoC (capitolul 4) ce folosesc cu 10 porti logice decat sintezele realizate cu Leonardo Spectrum si cu 20-30 decat cele realizate cu XST. Daca combinam programul Synplify Pro cu utilitarul Amplify FPGA, numarul total de porti logice poate sa scada cu inca 15-20

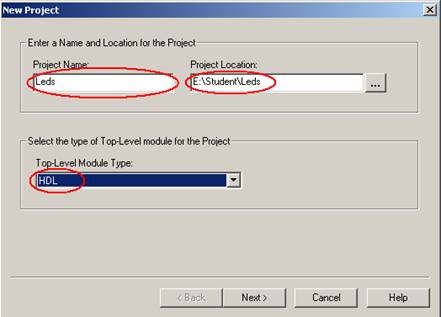

3 Exemplu practice de aplicatie folosind XC3S200 si XC2S200

Se va porni mediul de dezvoltare "Xilinx ISE 7.1"

Din meniu se va alege File -> New Project

Se vor completa numele, locatia si tipul modulului principal:

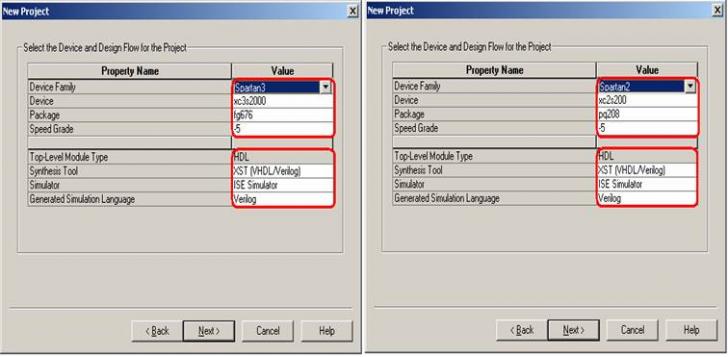

Se va completa tipul de FPGA tinta, tipul modulului principal, instrumentul de sinteza, simulatorul precum si tipul limbajului simulat:

Se va alege optiunea Next pana la generarea completa a proiectului.

In continuare vom incerca dezvoltarea unui program pentru aprinderea celor 8 leduri, cate unul odata.

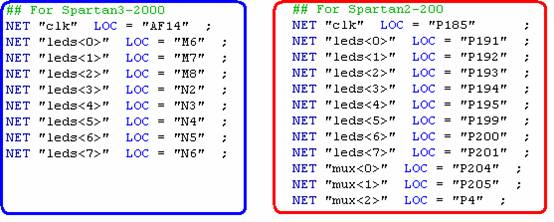

Iesirile FPGA pentru cele 8 leduri sunt:

|

XC3S2000 Signal |

XC3S2000 Out |

XC2S200 Signal |

XC2S200 Out |

|

Clk |

AF14 |

Clk |

P185 |

Led0 |

M6 |

Led0 |

P191 |

|

Led1 |

M7 |

Led1 |

P192 |

|

Led2 |

M8 |

Led2 |

P193 |

|

Led3 |

N2 |

Led3 |

P194 |

|

Led4 |

N3 |

Led4 |

P195 |

|

Led5 |

N4 |

Led5 |

P199 |

|

Led6 |

N5 |

Led6 |

P200 |

|

Led7 |

N6 |

Led7 |

P201 |

|

Mux0 |

Mux0 |

P204 |

|

|

Mux1 |

Mux1 |

P205 |

|

|

Mux2 |

Mux2 |

P4 |

Se va completa codul Verilog dupa cum urmeaza:

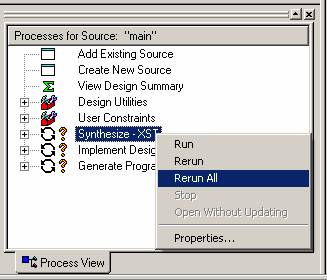

Se va sintetiza programul:

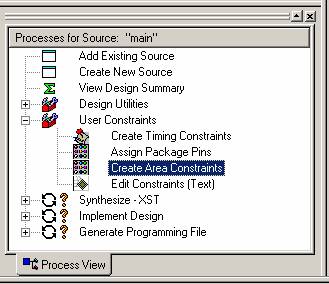

Se vor adauga constrangerile, folosindu-se editorul de constrangeri vizual, sau editorul de constrangeri in mod text:

Atentie! Verificati ca fisierul de constrangeri contine:

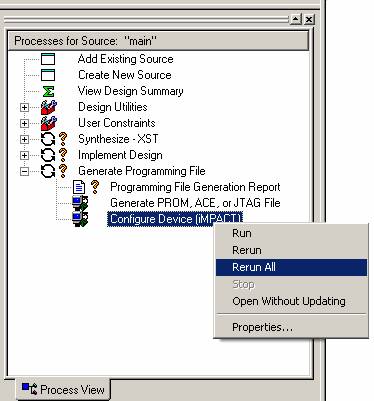

Se va genera BitStream-ul si se va incarca in FPGA (se va folosi programul Impact Configurator)

Teme de laborator:

if(leds_out == 8'hFF || leds_out == 8'h00)

leds_out = 8'hFE; //Spartan3-2000

respectiv

leds_out = 8'h01; //Spartan2-200

|

Politica de confidentialitate | Termeni si conditii de utilizare |

Vizualizari: 3109

Importanta: ![]()

Termeni si conditii de utilizare | Contact

© SCRIGROUP 2026 . All rights reserved